(продолжение работы над своим процессором, и в заголовке про физическую память так как везде поисковиком находится про ячейки Excell).

Сначала думал - да ну какая мелочь для процессора, но потом подумал - многие пишут о мелочах и даже получают плюсы, почему не написать о мелочи, если чип создаётся новый.

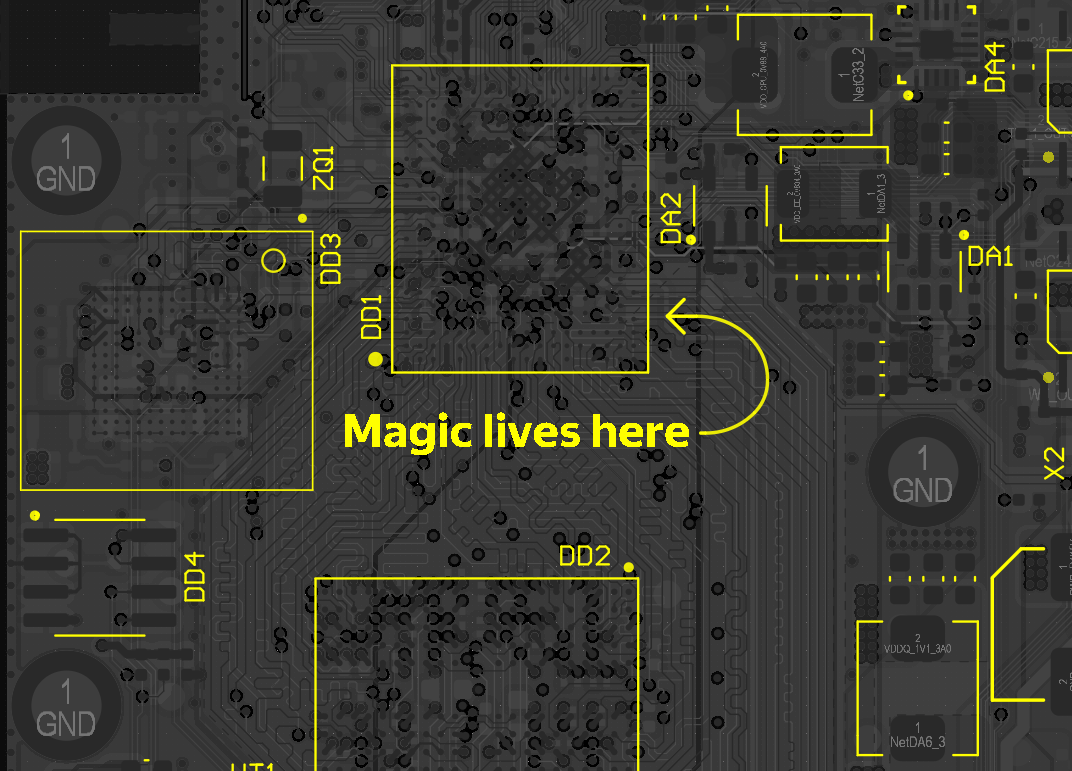

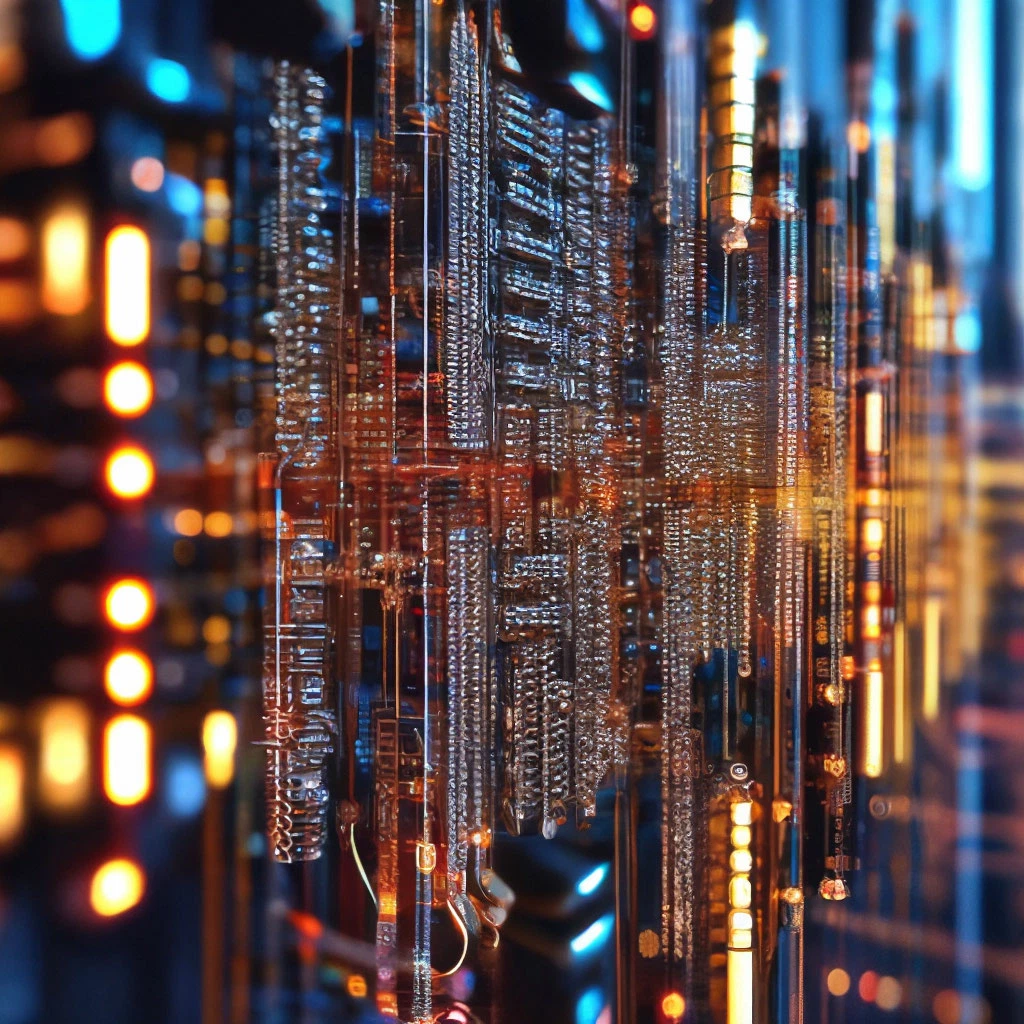

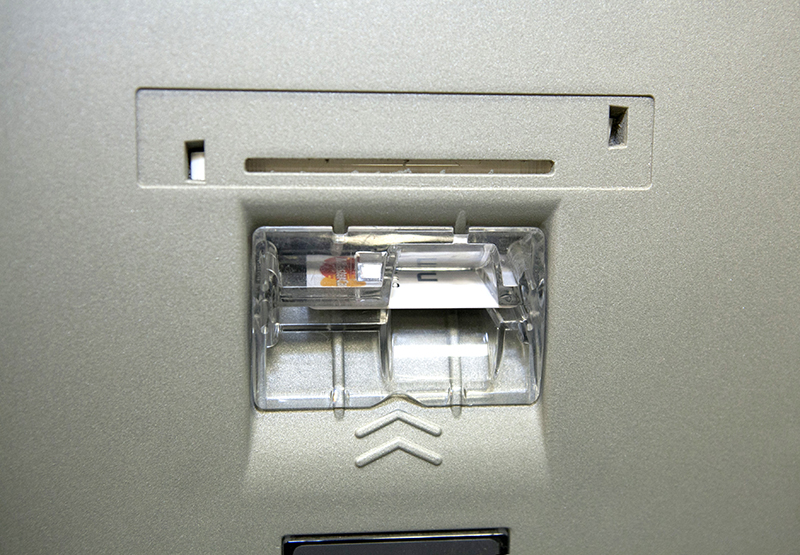

Сразу говорю, что роль памяти в данной схеме играют SR триггеры предполагаемого FPGA и процедура заполнения любого числа цепи ячеек (или даже одной) выполняется за два рабочих такта проектируемого процессора, независимо от числа выбранных ячеек. Над этой задачкой пришлось немного пломать голову, и нужно было понять что такое управляемый буфер (в данном случае это для Logisim Evolution).

После того, как составил рабочую схему кэша мостов, для работы процессора в режиме без счётчика команд, приступил к схеме управления кэшом мостов. Кэш мостов - это кэш обеспечивающий выполнение команд без счётчика команд, и позволяющий выполнять только команды в обозначенных ячейках памяти. По сути управление кэшем мостов сводится к мгновенному заполнению групп выбранных ячеек. И вот для того чтобы обеспечить бесперебойную работу управляемых буферов в сложной цепи (множество ячеек и множество источников сигнала) пришлось пойти на Хитрость с ИСКЛЮЧАЮЩИМ ИЛИ.

Триггеры группы Last - нижний ряд триггеров на данном изображении, служит для обозначения последнего триггера данной группы для конкретной ячейки, в который запишется единица и заблокирует прохождение сигнала по верхнему проводнику, через который подряд записывается единица в сами эти ячейки памяти механизма управления кэшем мостов - в триггеры группы Memo (незаконченное слово, так как по сути всё это является устройством для управления памятью, а не ей самой).