Всем привет!

В прошлой статье я запустил простой OpenCL пример на FPGA фирмы Altera:

// ACL kernel for adding two input vectors

__kernel void vector_add( __global const uint *restrict x,

__global const uint *restrict y,

__global uint *restrict z )

{

// get index of the work item

int index = get_global_id(0);

// add the vector elements

z[index] = x[index] + y[index];

}

Я намеренно не углублялся в детали и показал верхушку айсберга: процесс разработки, сборку проекта, запуск на системе.

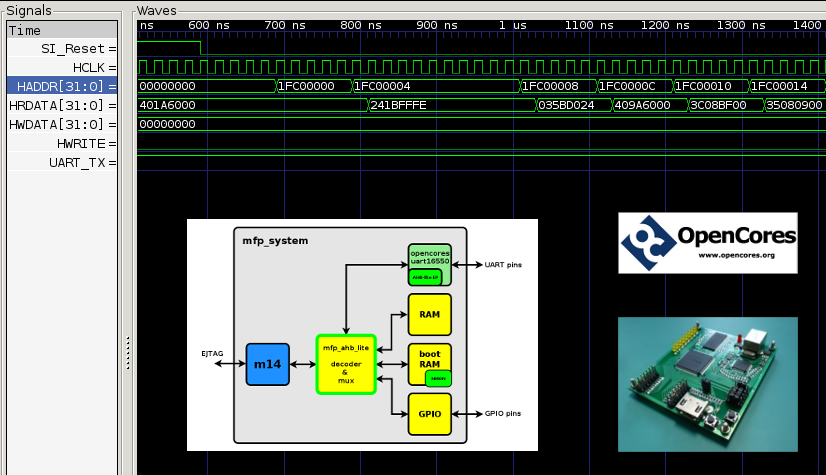

При подготовке первой статьи мне стало дико интересно, во что превращаются (со стороны FPGA) эти строчки. Понимание архитектуры даст возможность что-то соптимизировать и понять на что уходят ресурсы, а так же что хорошо и плохо для этой системы.

В этой статье мы попробуем вскрыть ядро и найти ответы на следующие вопросы:

- Какая у него архитектура?

- Как происходит его настройка? Как попадают данные на обработку?

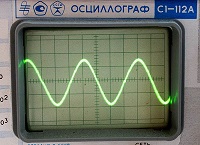

- На какой частоте он работает? Чем это определяется?

- Можно ли просимулировать только ядро в RTL-симуляторах?

- Какие блоки занимают больше всего ресурсов? Можно ли как-то это соптимизировать?

Давайте взглянём на его внутренности! Добро пожаловать под кат!

Недавно я увидел проект генератора сигналов на микроконтроллере AVR. Принцип генерации —

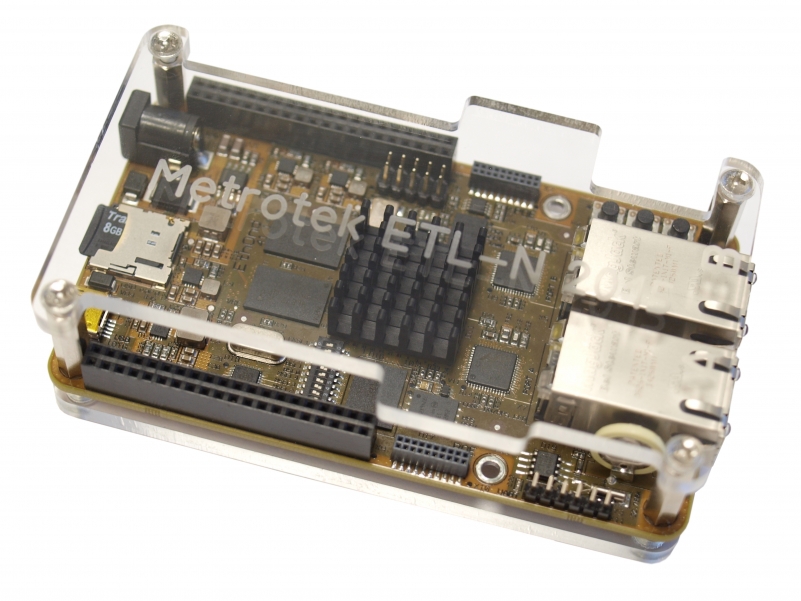

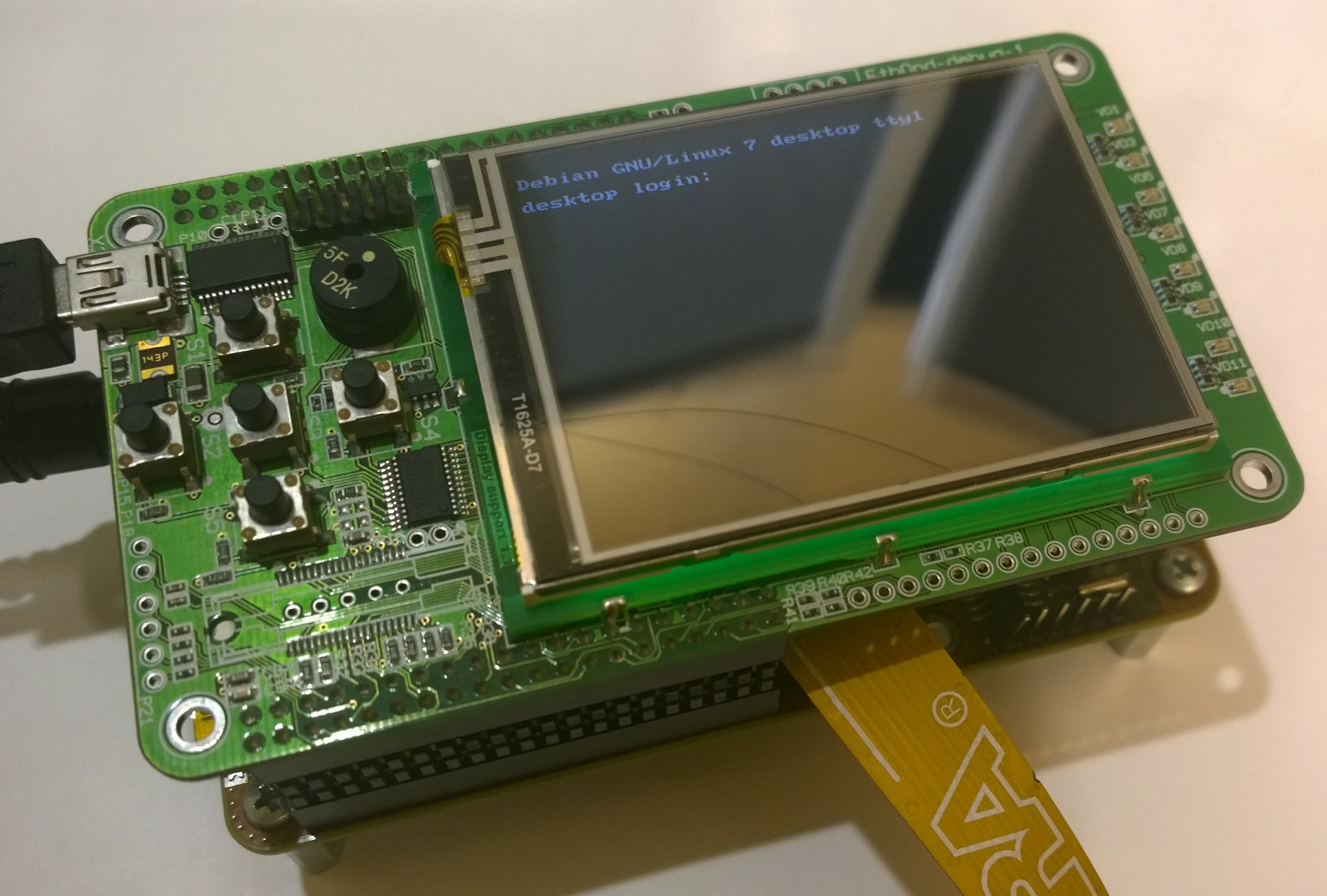

Недавно я увидел проект генератора сигналов на микроконтроллере AVR. Принцип генерации —  Недавно я все-таки сделал свой первый шаг к ПЛИС и

Недавно я все-таки сделал свой первый шаг к ПЛИС и